Description

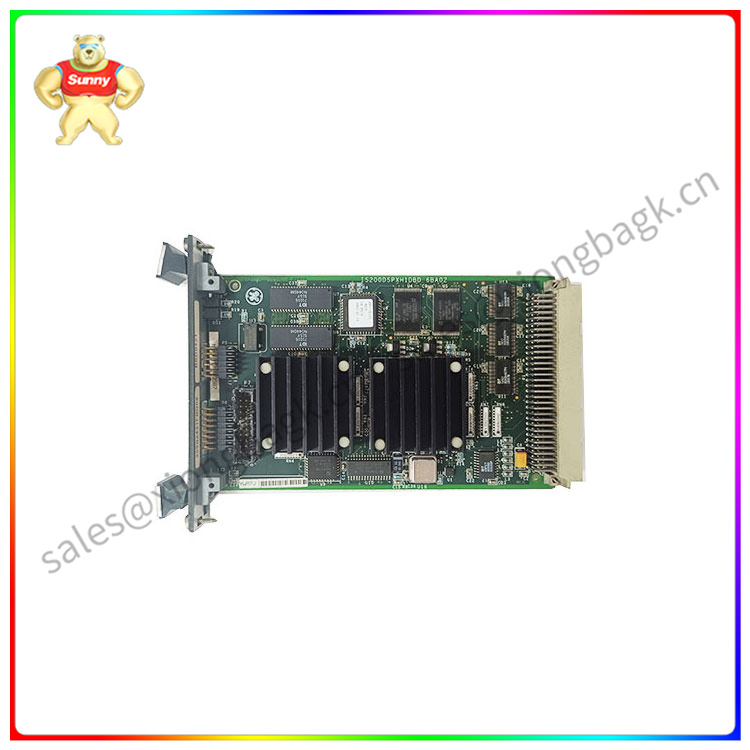

IS200DSPXH1D Digital Signal Processor Control Board (DSPX)

Part No.: IS200DSPXH1D

Manufacturer: General Electric

Country of Manufacture: United States (USA)

Product Type: Digital Signal Processor Control Board (DSPX)

Series: EX2100

IS200DSPXH1D is a Digital Signal Processor Control Board developed by GE. It is the primary

controller for the Innovation Series drives’ bridge, motor regulator, and gating operations. It also manages

the EX2100 Excitation Control’s generator field control functions. The logic, processing, and interface

functions are all provided by the board. The DSPX board is comprised of a high-performance digital signal

processor (DSP), standard memory components, and an application-specific integrated circuit (ASIC) that performs custom logic functions.

Standard Hardware Features

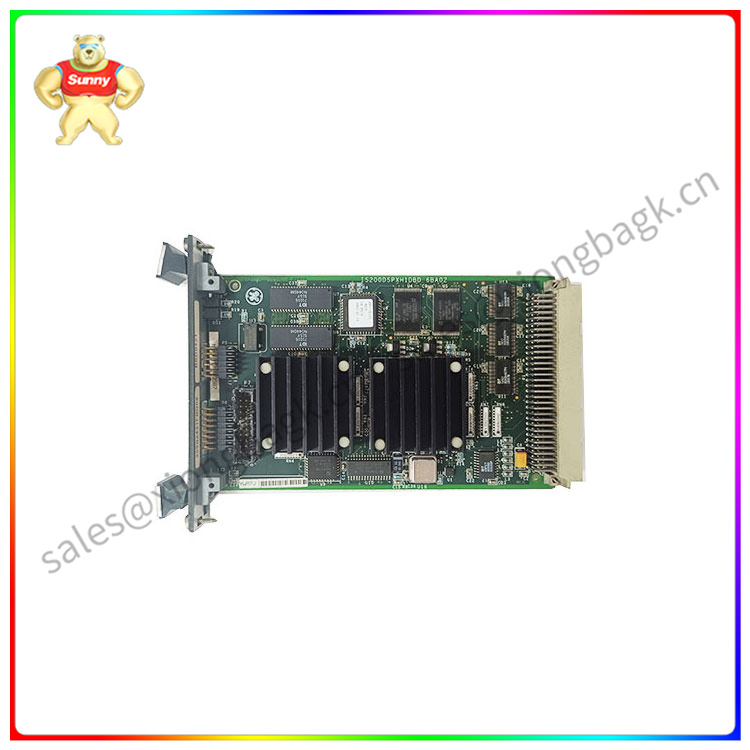

The Digital Signal Processor (DSP) of the DSPX runs at 60 MHz. There are four externals.

During normal operation, the DSP receives interrupts:

- Stack overflow (INT0)

- A load pulse in the inner loop (INT1)

- There are two inputs that can be customized (INT2, INT3)

The DSPX board supports the following types of memory:

- DSP boot images, code execution, configurable item storage, and system history records are all stored in FLASH memory.

- RAM is used to store data and run programs.

- NVRAM stands for nonvolatile random access memory.

- Add-only memory for identifying board revisions

IS200DSPXH1DBD

Both the foreground stack (from internal memory) and the background stack have overflow

detection (from external SRAM). If either stack overflows, an interrupt INT0 is generated. A hard reset is

generated if both stacks overflow. A configuration register is provided to disable the stack overflow reset. The

DSP activates and periodically toggles a watchdog timer (toggle interval is configurable). A watchdog timer

timeout will result in a hard reset. A free running timer of 24 bits is also provided and is used as a reference for certain functions.

As two quadrature incremental tach interfaces, five differential (HIFI) pair application inputs can be used (one

with marker capability). Two 16-bit up/down counters are driven by the signals. When the inputs are at the

same level, it maintains its current state; when the inputs are differentially opposite, it changes state. Each

time the counter increments or decrements, a 5 MHz timer resets, and a state register records the direction

of the last count. A capture register is associated with each of these counters, timers, and registers and can

be configured to capture the values on the occurrence of either the inner loop load pulse or the application loop load pulse.

The five differential HIFI inputs can be used as VCO counters in the application layer or as single-channel

tach interfaces. On the differentially decoded and filtered inputs, five 16-bit counters increment. The application

loop load pulse stores these counter values in registers that the DSP can read. Up to ten discrete inputs can be

used in addition to the five differential HIFI inputs. Each input is filtered for three system clock cycles before being read directly by the DSP into a buffer.

Please contact Sunny sales@xiongbagk.cn for the best price.

➱ sales manager: Sunny

➱ email mailto: sales@xiongbagk.cn

➱ Skype/WeChat: 18059884797

➱ phone/Whatsapp: + 86 18059884797

➱ QQ: 3095989363

➱ Website:www.sauldcs.com

Reviews

There are no reviews yet.